# **Dual-Rail Ultra-Low Dropout 1.5A LDO**

#### **General Description**

The ET5A4ADJZB is CMOS-based low-dropout, low-power linear regulators, offering 1500mA with NMOS pass transistor and a separate bias supply voltage(V<sub>BIAS</sub>). The device provides very stable, accurate output voltage with low noise, high ripple rejection and low supply current suitable for space constrained, noise sensitive application. ET5A4ADJZB consists of an accurate voltage-reference block, an error amplifier, a thermal-shutdown circuit, and a current limit circuit.

#### **Features**

Wide V<sub>IN</sub> Voltage Range: V<sub>OUT</sub>+0.15V to V<sub>BIAS</sub>

Wide V<sub>BIAS</sub> Voltage Range: 3.0V to 5.5V

Output Voltage Range: 0.5V to 3.0V

Very Low V<sub>BIAS</sub> Input Current: 60μA

Ultra Low Dropout: 80mV at 1.5A@V<sub>OUT</sub>=1V

Built-in Over-current Protection and Thermal Shutdown Circuit

Built-in Auto-discharging Circuit (optional)

Built-in Under Voltage Lock-out

Package Information:

| Part No.   | Package                                 | MSL     |  |

|------------|-----------------------------------------|---------|--|

| ET5A4ADJZB | WLCSP6 (1.31mm×0.875mm×0.31mm,0.4pitch) | Level 1 |  |

1

#### **Applications**

- Telecom Industrial and Consumer Equipment

- FPGA, DSP and Logic Power Supplies

- Switching Power Supply Post Regulation

- Specific Start-up Time or Sequencing Requirement Applications

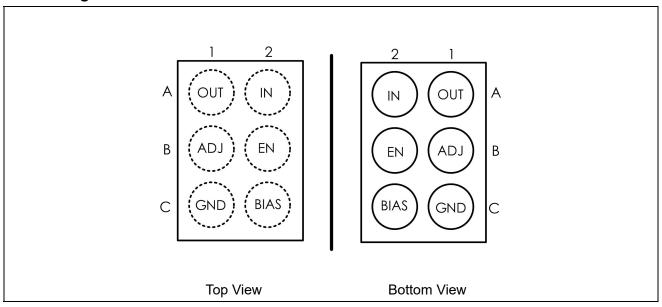

# Pin Configuration

## **Pin Function**

| Pin Name | Symbol | Pin Description                                                                 |  |

|----------|--------|---------------------------------------------------------------------------------|--|

| A1 OUT   |        | The power output of the device.                                                 |  |

| A1       | 001    | A 22µF (typ.) ceramic capacitor is recommended at this pin.                     |  |

| A2       | IN     | Input voltage Pin. Large bulk capacitance should be placed closely to this pin. |  |

| AZ       | IIN    | A 10μF (typ.) ceramic capacitor is recommended at this pin.                     |  |

| D4 AD1   |        | ADJ Adjustable Regulator Feedback Input. Connect to output voltage resistor     |  |

| B1       | ADJ    | divider central node.                                                           |  |

| B2       | EN     | Enable Input.                                                                   |  |

| C1       | GND    | Ground pin.                                                                     |  |

| C2       | BIAS   | Input voltage for controlling circuit.                                          |  |

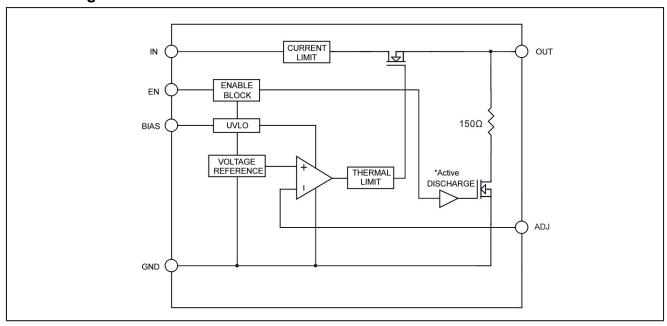

#### **Block Diagram**

#### **Functional Description**

The ET5A4ADJZB dual-rail very low dropout voltage regulator is using NMOS pass transistor for output voltage regulation from  $V_{\text{IN}}$  voltage. All the low current internal control circuitry is powered from the  $V_{\text{BIAS}}$  voltage.

The use of an NMOS pass transistor offers several advantages in applications. Unlike PMOS topology devices, the output capacitor has reduced impact on loop stability.  $V_{IN}$  to  $V_{OUT}$  operating voltage difference can be very low compared with standard PMOS regulators in very low  $V_{IN}$  applications.

The ET5A4ADJZB offers smooth start-up.

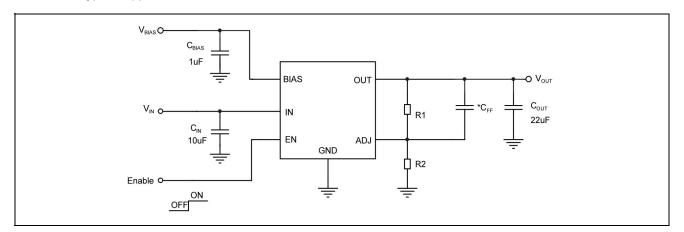

#### **Input and Output Capacitor**

The device is designed to be stable for ceramic output capacitors with  $22\mu F$  capacitance. The device is also stable with multiple capacitors in parallel. In applications where no low input supplies impedance available (PCB inductance in  $V_{IN}$  and/or  $V_{BIAS}$  inputs as example), the recommended  $C_{IN}$  =10 $\mu F$  and  $C_{BIAS}$ = 1 $\mu F$  or greater.

#### **Enable Pin Operation**

The ET5A4ADJZB is turned on by setting the EN pin to "H". The threshold limits are covered in the electrical characteristics table in this datasheet. When the EN pin is not used, connect the EN pin with  $V_{BIAS}$  to keep the LDO in operating mode.

#### **Current Limit Protection**

When output current of  $V_{OUT}$  pin is higher than current limit threshold or the  $V_{OUT}$  pin is direct short to GND, the current limit protection will be triggered and clamp the output current at a predesigned level to prevent over-current and thermal damage.

#### **Thermal Shutdown Protection**

Thermal protection disables the output when the junction temperature rises to approximately +160°C, allowing the device to cool down. When the junction temperature reduces to approximately +140°C the output circuit is enabled again. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the heat dissipation of the regulator, protecting it from damage due to overheating.

#### **Auto Discharging**

When the EN pin set to "L", the output circuit will be disable immediately, and the Auto-Discharging circuit will be turned on to discharge the electric charge on output capacitor, and decrease the voltage of V<sub>OUT</sub> in very short time.

#### **Output Voltage Adjust**

The required output voltage of Adjustable devices can be adjusted from  $V_{REF}$  to 3.0 V using two external resistors. Typical application schematics is shown blow.

$V_{OUT} = V_{REF} \times (1+R1/R2)$

Typical value of  $V_{REF}$  (ADJ Pin) is 0.5. It is recommended to keep the total serial resistance of resistors (R1 + R2) no greater than  $100k\Omega$ .

The output voltage needs to take into account the error caused by the resistance accuracy.

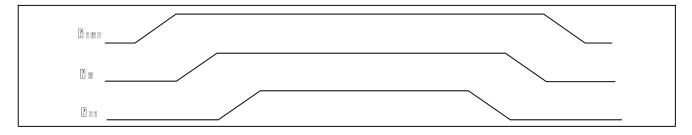

#### **Power Up/Down Sequence Control**

The recommended power on sequence of ET5A4ADJZB is to power on  $V_{SYS}$  first, then power on input power  $V_{IN}$ , then set  $V_{EN}$  to high level, and then enable LDO. The corresponding power off sequence is to turn off LDO. First, set  $V_{EN}$  to low level, then power off input power  $V_{IN}$ , and finally power off  $V_{SYS}$ .

# **Absolute Maximum Ratings**

| Symbol               | Item                                 | Rating      | Unit |

|----------------------|--------------------------------------|-------------|------|

| $V_{IN}$             | Input Voltage(IN Pin)                | -0.3 to 6.0 | V    |

| V <sub>BIAS</sub>    | Input Voltage (BIAS Pin)             | -0.3 to 6.0 | V    |

| V <sub>EN</sub>      | Input Voltage (EN Pin)               | -0.3 to 6.0 | V    |

| $V_{FB}$             | Input Voltage (FB Pin)               | -0.3 to 6.0 | V    |

| V <sub>OUT</sub>     | Output Voltage(OUT Pin)              | -0.3 to 6.0 | V    |

| I <sub>OUT_MAX</sub> | Maximum Load Current                 | 1500        | mA   |

| D                    | Maximum Power Consumption            | 1500        | m/\/ |

| P <sub>D_MAX</sub>   | (PCB: 5cm × 5cm, 2layer, 1oz )       | 1500        | mW   |

| T <sub>J_MAX</sub>   | Maximum Junction Temperature         | -40 to 150  |      |

| T <sub>STG</sub>     | Storage Temperature Range            | -65 to +150 | °C   |

| TL                   | Lead Temperature (Soldering, 10 sec) | 260         | °C   |

| R <sub>θJA</sub>     | Thermal Resistance, Junction-to-Air  | 66.6        | °C/W |

| \/                   | HBM (EIA/JESD22-A114-A)              | ±2000       | V    |

| V <sub>ESD</sub>     | CDM (EIA/JESD22-C101-A)              | ±1500       | V    |

# **Recommended Operating Conditions**

| Symbol            | ltem                                     | Rating                                   | Unit |

|-------------------|------------------------------------------|------------------------------------------|------|

| V <sub>IN</sub>   | IN Input Voltage                         | V <sub>OUT</sub> +0.15 to                | V    |

| VIN               | IN Input Voltage                         | 5.5 &V <sub>IN</sub> <v<sub>BIAS</v<sub> | V    |

| V                 | PIAS Input Voltage                       | 3 to 5.5 & V <sub>BIAS</sub>             | V    |

| V <sub>BIAS</sub> | BIAS Input Voltage                       | >V <sub>OUT</sub> +1.6V                  | V    |

| l <sub>оит</sub>  | Output Current                           | 0 to 1500                                | mA   |

| T <sub>A</sub>    | Operating Ambient Temperature            | -40 to 85                                | °C   |

| TJ                | Operating Junction Temperature           | -40 to 125                               | °C   |

| C <sub>IN</sub>   | Effective Input Ceramic Capacitor Value  | 4.7 to 22                                | μF   |

| C <sub>BIAS</sub> | Effective Input Ceramic Capacitor Value  | 0.22 to 4.7                              | μF   |

| Соит              | Effective Output Ceramic Capacitor Value | 6.8 to 33                                | μF   |

| ECD               | Input and Output Capacitor Equivalent    | 5 to 100                                 | 0    |

| ESR               | Series Resistance                        | 5 to 100                                 | mΩ   |

### **Electrical Characteristics**

(Unless otherwise noted,  $V_{IN}=V_{OUT}+0.3V$ ,  $V_{BIAS}=3.0V$ ,  $I_{OUT}=1mA$ ,  $C_{IN}=10\mu F$ ,  $C_{OUT}=22\mu F$ ,  $C_{BIAS}=1\mu F$ ,  $T_A=-40\sim+85^{\circ}C$ . Typical values are at  $T_A=25^{\circ}C$ )

| Symbol                         | Parameter                                        | Test Conditions                                                    | Min                | Тур                     | Max               | Unit  |

|--------------------------------|--------------------------------------------------|--------------------------------------------------------------------|--------------------|-------------------------|-------------------|-------|

| ) / (1)                        | L()// H D                                        | V >V 0.45V T - 0500                                                | V <sub>OUT</sub> + |                         | 5.5&<             |       |

| V <sub>IN</sub> <sup>(1)</sup> | Input Voltage Range                              | V <sub>IN</sub> ≥V <sub>OUT</sub> +0.15V, T <sub>A</sub> =25°C     | 0.15V              |                         | V <sub>BIAS</sub> | V     |

| $V_{BIAS}$                     | V <sub>BIAS</sub> Voltage Range                  | V <sub>BIAS</sub> >3.0 & V <sub>BIAS</sub> > V <sub>OUT</sub> +1.6 | 3.0                |                         | 5.5               | V     |

| Vuvlo                          | Under veltage leek out                           | V <sub>BIAS</sub> Rising                                           | 1.50               | 1.80                    | 2.10              | V     |

| V <sub>UVLO_HYS</sub>          | Under-voltage lock-out                           | Hysteresis                                                         | 0.10               | 0.26                    | 0.45              | V     |

| $I_{Q_ON}$                     | V <sub>BIAS</sub> Current                        | Active mode: V <sub>EN</sub> =V <sub>BIAS</sub>                    | 40                 | 60                      | 100               | μA    |

| $I_{Q_OFF}$                    | VBIAS CUITEIII                                   | V <sub>EN</sub> =0V                                                |                    | 1.0                     | 3                 | μA    |

| $V_{FB}$                       | FB Voltage                                       | T <sub>A</sub> =25 °C                                              | 0.495              |                         | 0.505             | V     |

| V <sub>OUT</sub>               | Output Voltage                                   |                                                                    | 0.5                |                         | 3.0               | V     |

| V <sub>DROP</sub> (2)          | Dropout Voltage                                  | I <sub>OUT</sub> =1500mA, V <sub>OUT</sub> =1.0V                   |                    | 80                      | 160               | mV    |

| I <sub>LIM</sub>               | Current Limit                                    | V <sub>IN</sub> =V <sub>OUT</sub> +0.2V, T <sub>A</sub> =25°C      |                    | 4                       |                   | Α     |

| I <sub>SHORT</sub>             | Short Current Limit                              | V <sub>OUT</sub> =0V                                               |                    | 1500                    |                   | mA    |

| Regload                        | Load Regulation                                  | 1mA ≤ I <sub>OUT</sub> ≤ 1500mA                                    |                    | 4                       | 30                | mV    |

|                                |                                                  | V <sub>OUT</sub> =1.0V                                             |                    |                         |                   |       |

|                                | V <sub>IN</sub> Line Regulation                  | $V_{OUT}+0.3V \le V_{IN} \le 5V$<br>$V_{OUT}=1.0V$                 |                    | 0.01                    | 0.1               | %/V   |

| Reg <sub>LINE</sub>            |                                                  | 3.0V <v<sub>BIAS&lt;5.5V,</v<sub>                                  |                    |                         | -                 |       |

|                                | V <sub>BIAS</sub> Line Regulation                | (V <sub>BIAS</sub> >V <sub>OUT</sub> +1.6) V <sub>OUT</sub> =1.0V  |                    | 0.01                    | 0.1               |       |

|                                |                                                  | V <sub>IN</sub> to V <sub>OUT</sub> , f=1kHz,                      |                    |                         |                   |       |

|                                | Ripple Rejection                                 | $V_{IN}=V_{OUT}+0.5V$ , $V_{OUT}=1.0V$ ,                           |                    | 70                      |                   |       |

| DCDD(3)                        |                                                  | Ripple 0.2Vp-p, I <sub>OUT</sub> =30mA                             |                    |                         |                   | 40    |

| PSRR <sup>(3)</sup>            |                                                  | V <sub>BIAS</sub> to V <sub>OUT</sub> , f=1kHz,                    |                    |                         |                   | dB    |

|                                |                                                  | $V_{IN}$ = $V_{OUT}$ +0.5 $V$ , $V_{OUT}$ =1.0 $V$ ,               |                    | 70                      |                   |       |

|                                |                                                  | Ripple 0.2Vp-p, I <sub>OUT</sub> =30mA                             |                    |                         |                   |       |

|                                |                                                  | $V_{IN}=V_{OUT}+0.5V$ ,                                            |                    | 60*                     |                   | μVRMS |

| e <sub>N</sub> <sup>(3)</sup>  | Output Noise                                     | f=10 Hz to 100 kHz,                                                |                    | 60*<br>V <sub>оит</sub> |                   |       |

|                                |                                                  | I <sub>OUT</sub> =1mA                                              |                    | V OUT                   |                   |       |

| I <sub>EN</sub>                | EN Pull-down Current                             | V <sub>EN</sub> =5.5V, V <sub>BIAS</sub> =5.5V                     |                    |                         | 3                 | μA    |

| V <sub>ENH</sub>               | EN Input Voltage High                            |                                                                    | 1.0                |                         |                   | V     |

| V <sub>ENL</sub>               | EN Input Voltage Low                             |                                                                    |                    |                         | 0.4               | V     |

| R <sub>DIS</sub>               | Output resistance of auto discharge at off state | V <sub>EN</sub> =0V, V <sub>OUT</sub> =0.5V                        |                    | 150                     | 250               | Ω     |

### **Electrical Characteristics(Continued)**

(Unless otherwise noted,  $V_{IN}=V_{OUT}+0.3V$ ,  $V_{BIAS}=3.0V$ ,  $I_{OUT}=10mA$ ,  $C_{IN}=10\mu F$ ,  $C_{OUT}=22\mu F$ ,  $C_{BIAS}=1\mu F$ ,

$T_A=-40\sim+85$ °C. Typical values are at  $T_A=25$  °C)

|                                 |                  | I <sub>OUT</sub> =1mA to 1500mA in 10us                         |  | 65*              | 90*  | mV |

|---------------------------------|------------------|-----------------------------------------------------------------|--|------------------|------|----|

| V <sub>TRLD</sub> (3)           | Load Transient   | V <sub>IN</sub> = V <sub>OUT</sub> +0.2V, T <sub>A</sub> =25°C  |  | Vouт             | Vout |    |

|                                 |                  | I <sub>OUT</sub> =1500mA to 1mA in 10us                         |  | 65*              | 90*  | mV |

|                                 |                  | V <sub>IN</sub> = V <sub>OUT</sub> +0.2V, T <sub>A</sub> =25 °C |  | V <sub>OUT</sub> | Vout |    |

|                                 |                  | V <sub>OUT</sub> =1.0V,                                         |  |                  |      |    |

| T <sub>ON</sub>                 | Turn-On Time     | From assertion of V <sub>EN</sub> to                            |  | 320              |      | μs |

|                                 |                  | V <sub>OUT</sub> =90%V <sub>OUT(NOM)</sub>                      |  |                  |      |    |

|                                 |                  | V <sub>OUT</sub> =1.0V,                                         |  |                  |      |    |

| T <sub>R</sub>                  | Rise Time        | From assertion of V <sub>OUT</sub> =10%                         |  | 200              |      | μs |

|                                 |                  | to 90%V <sub>OUT(NOM)</sub>                                     |  |                  |      |    |

| T <sub>TSD</sub> <sup>(3)</sup> | Thermal Shutdown | T vision                                                        |  | 160              |      | သိ |

|                                 | Threshold        | T <sub>J</sub> rising                                           |  | 100              |      | J  |

| T <sub>HYS</sub> (3)            | Thermal Shutdown | T. folling from chutdown                                        |  | 20               |      | သိ |

|                                 | Hysteresis       | T <sub>J</sub> falling from shutdown                            |  | 20               |      |    |

#### Notes:

1: The maximum input voltage should take into account the maximum power consumption (PD(max)). The calculation formula is as follows:

$$P_D(max) = (V_{IN}(max) - V_{OUT}) \times I_{OUT}$$

The maximum power consumption of the circuit is 1500mW.

$$V_{IN}(max) = 1500mW / I_{OUT} + V_{OUT}$$

7

For example:

If  $V_{OUT}$ = 1.0V,  $I_{OUT}$  =1000mA, The maximum input voltage is  $V_{IN}$ (max)=1500mW/1000mA+1.0=2.5V

- **2**:  $V_{DROP}$  FT test method: test the  $V_{OUT}$  voltage at  $V_{SET}$ + $V_{DROPMAX}$  with output current.

- 3: Guaranteed by design and characterization, not a FT item.

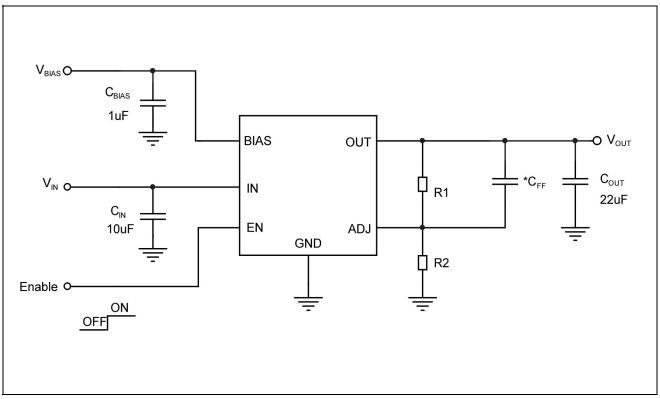

## **Application Circuits**

**Note\***:  $V_{OUT} = 0.5 \times (1 + R1/R2)$ , (R1+R2) no greater than 100kΩ. The feedforward capacitor  $C_{FF}$  is optional for the optimization of transient response, suggested value is 10nF.

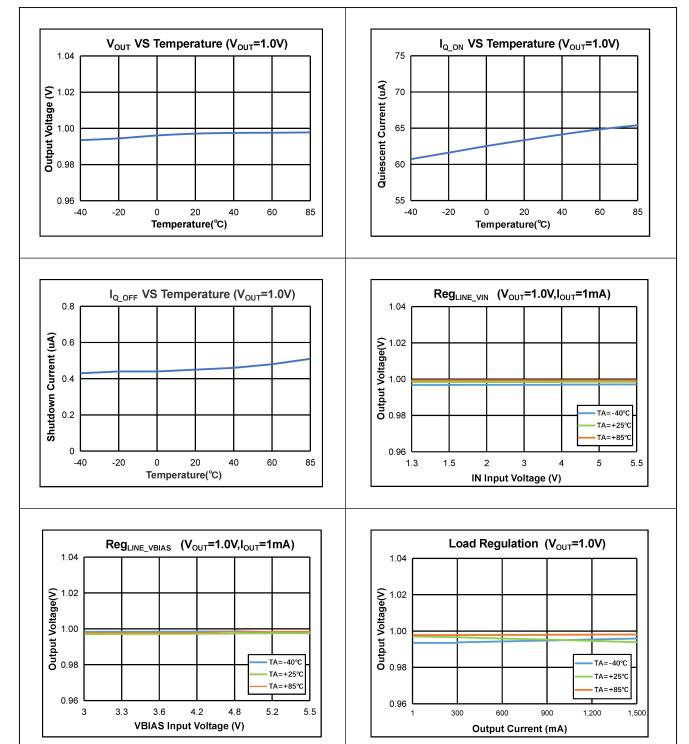

### **Typical Characteristics**

Note: Typical Characteristics are intended to be used as reference data; they are not guaranteed.

(  $V_{IN}$ =1.30V,  $V_{BIAS}$ = 3.0V,  $I_{OUT}$ =1mA,  $C_{IN}$ =10 $\mu$ F, $C_{OUT}$ =22 $\mu$ F,  $C_{BIAS}$ =1 $\mu$ F,  $V_{OUT}$ =1V)

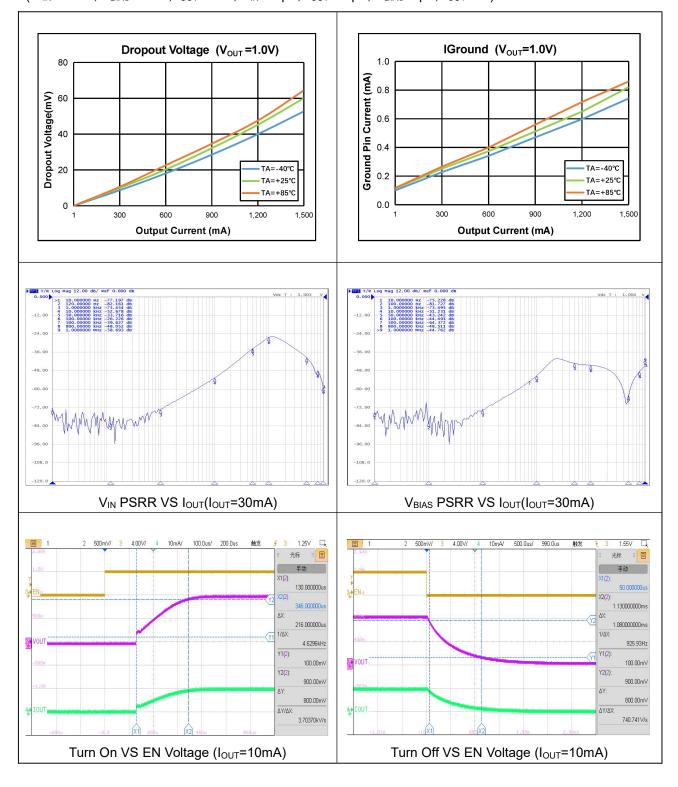

### **Typical Characteristics (Continued)**

Note: Typical Characteristics are intended to be used as reference data; they are not guaranteed. ( $V_{IN}=1.30V$ ,  $V_{BIAS}=3.0V$ ,  $I_{OUT}=1mA$ ,  $C_{IN}=10\mu F$ ,  $C_{OUT}=22\mu F$ ,  $C_{BIAS}=1\mu F$ ,  $V_{OUT}=1V$ )

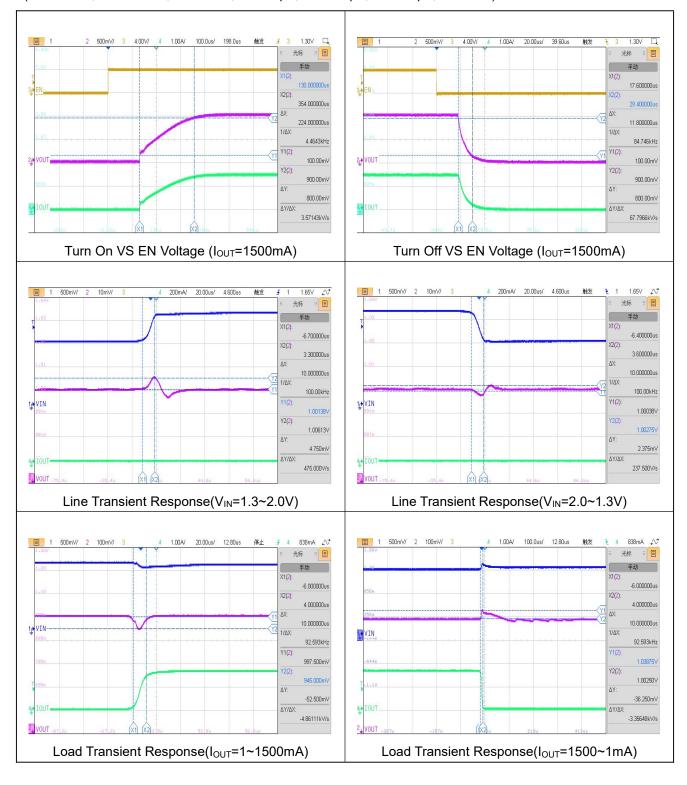

### **Typical Characteristics (Continued)**

Note: Typical Characteristics are intended to be used as reference data; they are not guaranteed. ( $V_{IN}=1.30V$ ,  $V_{BIAS}=3.0V$ ,  $I_{OUT}=1mA$ ,  $I_{OUT}=1mA$ ,  $I_{OUT}=10\mu F$ ,  $I_{OUT}=22\mu F$ ,  $I_{OUT}=1\mu F$ ,  $I_{OUT}=1V$ )

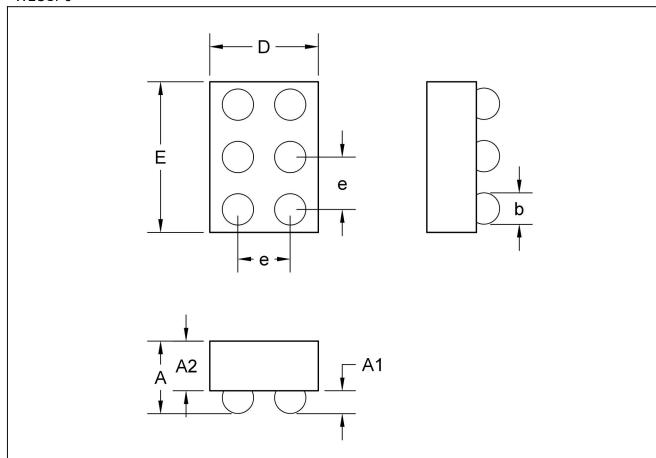

# **Package Dimension**

## WLCSP6

## **Dimensions Table (Units: mm)**

| Symbol | Min       | Nom   | Max   |  |

|--------|-----------|-------|-------|--|

| Α      | 0.28      | 0.31  | 0.34  |  |

| A1     | 0.05      | 0.06  | 0.07  |  |

| A2     | 0.23      | 0.25  | 0.27  |  |

| b      | 0.26      | 0.27  | 0.28  |  |

| D      | 0.855     | 0.875 | 0.895 |  |

| Е      | 1.29      | 1.31  | 1.33  |  |

| е      | 0.400 BSC |       |       |  |

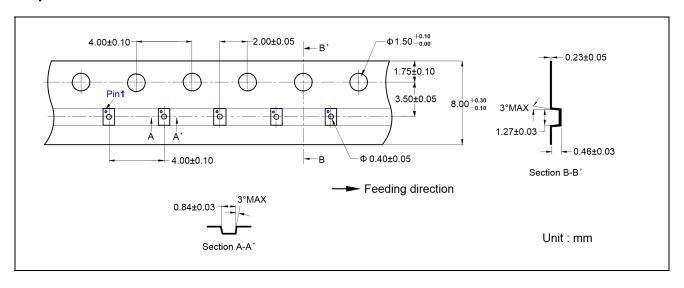

## **Tape Information**

## **Marking Information**

## **Revision History and Checking Table**

| Version | Date       | Revision Item                                               | Modifier | Function & Spec Checking | Package & Tape Checking |

|---------|------------|-------------------------------------------------------------|----------|--------------------------|-------------------------|

| 0.0     | 2022-11-22 | Preliminary Version                                         | Tugz     | Liuxm                    | Liujy                   |

| 1.0     | 2023-04-12 | Official Version                                            | Tugz     | Liuxm                    | Liujy                   |

| 1.1     | 2024-12-21 | Update Electrical Characteristics & Typical Characteristics | Pengjj   | Liuxm                    | Liujy                   |