## ET63HS42XX - High Input Very-Low IQ 300mA LDO

### **General Description**

The ET63HS42XX is a low dropout with 300mA load ability with enable function LDO. It operates from 3V  $\sim$  40V. The quiescent current is 5 $\mu$ A with no load. The devices feature integrated short-circuit and over-current protection. They are quite suitable for standby microprocessor control-unit systems, especially in automotive applications.

ET63HS42XX are available in the ESOP8 package.

#### **Features**

- Input Voltage Range from 3V to 40V

- 300mA Load Current

- I<sub>Q</sub> is 7μA Typical

- Low Dropout is 500mV at 300mA Load@Vout=3.3V

- Power-Good Feature is Available

- Over-Temperature Protection

- Current-Limit Protection

- Part No. and Package

| Part No. Package |       | Packing Option    | MSL |  |

|------------------|-------|-------------------|-----|--|

| ET63HS42XX       | ESOP8 | Tape and Reel, 4K | 3   |  |

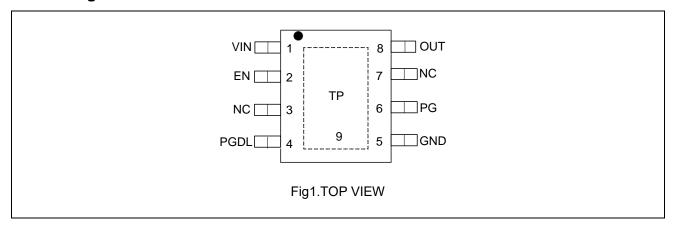

## **Pin Configuration**

### **Pin Function**

| Pin No. | Pin Name | Pin Function     |

|---------|----------|------------------|

| 1       | VIN      | Input Pin        |

| 2       | EN       | Enable Input Pin |

| 3,7     | NC       | No Connect       |

| 4       | PGDL     | PG Delay Pin     |

| 5       | GND      | Ground Pin       |

| 6       | PG       | Power Good Pin   |

| 8       | OUT      | Output Pin       |

| 9       | TP       | Thermal Pad      |

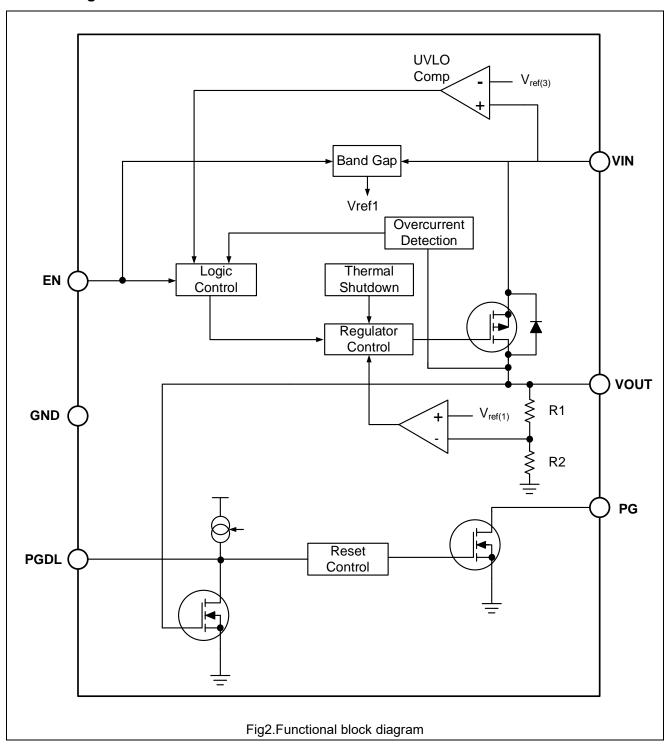

### **Block Diagram**

#### **Functional Description**

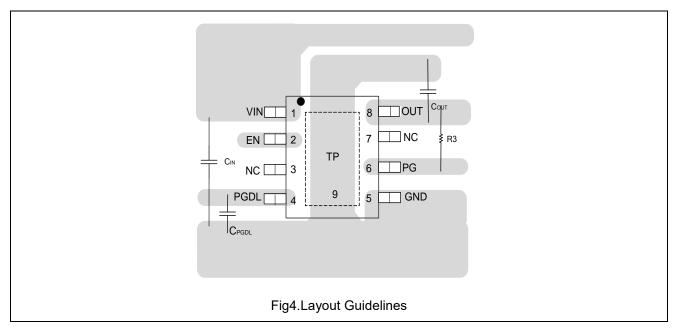

#### **Input Capacitor**

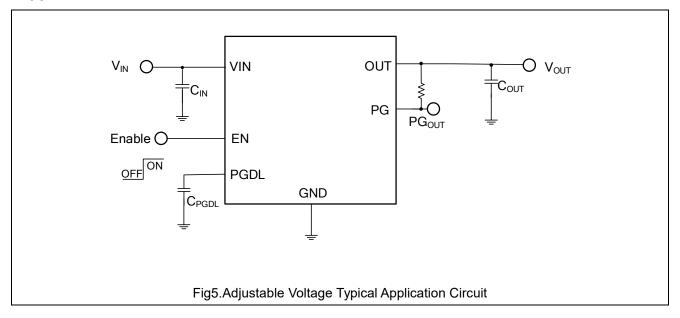

A  $2.2\mu F\sim 10\mu F$  ceramic capacitor is recommended to connect between  $V_{IN}$  and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. This input capacitor must be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both  $V_{IN}$  and GND.

#### **Output Capacitor**

An output capacitor is required for the stability of the LDO. The recommended output capacitance is from  $2.2\mu F$  to  $10\mu F$ , Equivalent Series Resistance (ESR) is from  $5m\Omega$  to  $100m\Omega$ , and temperature characteristics are X7R or X5R. Higher capacitance values help to improve load/line transient response. The output capacitance may be increased to keep low undershoot/overshoot. Place output capacitor as close as possible to OUT and GND pins.

#### **Enable**

TheET63HS42XX delivers the output power when it is set to enable state. When it works in disable state, there is no output power and the operation quiescent current is almost zero. The enable pin (EN) is active high.

#### **Dropout Voltage**

The ET63HS42XX uses a PMOS pass transistor to achieve low dropout. When  $(V_{IN} - V_{OUT})$  is less than the dropout voltage  $(V_{DROP})$ , the PMOS pass device is in the linear region of operation and the input-to-output resistance is the  $R_{DS(ON)}$  of the PMOS pass element.  $V_{DO}$  scales approximately with output current because the PMOS device behaves like a resistor in dropout mode. As with any linear regulator, PSRR and transient response degrade as  $(V_{IN} - V_{OUT})$  approaches dropout operation.

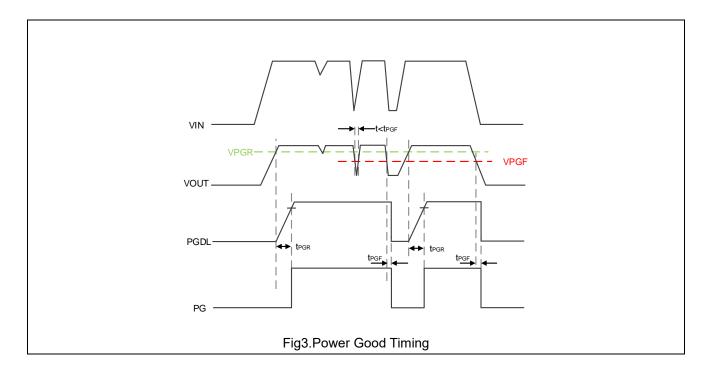

#### **Power Good**

The ET63HS42XX provides an open-collector PG Pin. The pin indicating output voltage regulation can be connected to VOUT through an external resistor. When VOUT is higher than the power on reset threshold, after a power on reset delay time, VPG is pulled up to a high level through an external resistor.

If it is not necessary to only regulate the output voltage, the pin can be open.

#### **Power Good Delay**

The external capacitor on PGDL pin sets a timer delay before releasing the reset pin high level. A constant output current charges the external capacitor until the voltage exceeds the threshold to trip the internal comparator. If the pin is open, the default delay time is 400µs (typical value). After setting the PG pin low, the capacitor on this pin discharges, allowing the capacitor to charge from approximately 0.2 V, delaying the timing for the next power on reset. When V<sub>OUT</sub> rises 90% of V<sub>OUT</sub>, the PG Pin is pulled to high by V<sub>OUT</sub>. The delay time (t<sub>PGDL</sub>) can be defined by adding a capacitor (C<sub>PGDL</sub>) on PGDL through below equation:

$t_{PGDL}=C_{PGDL} \times 1V /20nA$

#### **Thermal Shutdown**

Thermal shutdown protection disables the output when the junction temperature rises to approximately 155°C. Disabling the device eliminates the power dissipated by the device, allowing the device to cool. When the junction temperature cools to approximately 130°C, the output circuitry is again enabled.

Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits regulator dissipation, protecting the LDO from damage as a result of overheating. Activating the thermal shutdown feature usually indicates excessive power dissipation as a result of the product of the  $(V_{IN} - V_{OUT})$  voltage and the load current. For reliable operation, limit junction temperature to 150°C maximum.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance. For recommended operating conditions the maximum junction temperature is 150°C and  $T_A$  is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$  is layout dependent. The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance( $\theta_{JA}$ ).

#### **Current-Limit Protection**

The ET63HS42XX provides current limit function to prevent the device from damages during over-load or shorted-circuit condition. This current is detected by an internal sensing transistor.

### **Layout Guidelines**

- Place input and output capacitors as close to the device as possible.

- Use copper planes for device connections in order to optimize thermal performance.

- Place thermal vias around the device to distribute heat.

### **Absolute Maximum Ratings**

| Symbol              | Rating                       | Value                                      | Unit |

|---------------------|------------------------------|--------------------------------------------|------|

| VIN                 | Input Voltage <sup>(1)</sup> | -0.3~45 & V <sub>IN</sub> >V <sub>EN</sub> | V    |

| Vout                | Output Voltage               | -0.3~40                                    | V    |

| Ven                 | Chip Enable Input Voltage    | -0.3~V <sub>IN</sub>                       | V    |

| $V_{PG}$            | Power Good Voltage           | -0.3~Vоит                                  | V    |

| V <sub>PGDL</sub>   | Power Good Delay Voltage     | -0.3~5                                     | V    |

| T <sub>J(MAX)</sub> | Maximum Junction Temperature | 150                                        | °C   |

| T <sub>STG</sub>    | Storage Temperature          | -65~150                                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. **Note1**. Refer to Electrical Characteristics and Application Information for Safe Operating Area and IN port needs to be powered on before the EN port.

### **Thermal Characteristics**

| Symbol            | Ratings                                                      | Value | Unit |

|-------------------|--------------------------------------------------------------|-------|------|

| R <sub>θ</sub> JA | Thermal Characteristics, Thermal Resistance, Junction-to-Air | 60    | °C/W |

| P <sub>D</sub>    | Max Power Dissipation @25°C                                  | 2     | W    |

### **Recommended Operating Conditions**

| Symbol           | Item                                                          | Rating     | Unit |

|------------------|---------------------------------------------------------------|------------|------|

| V <sub>IN</sub>  | Input Voltage                                                 | 3 to 40    | V    |

| l <sub>out</sub> | Output Current                                                | 0 to 300   | mA   |

| TJ               | Operating Junction Temperature                                | -40 to 125 | °C   |

| Cin              | Input Capacitor Value                                         | 2.2 to 10  | μF   |

| Соит             | Output Capacitor Value                                        | 2.2 to 10  | μF   |

| $R_{PG}$         | Pull-up resistor of Power-Good                                | 1 to 100   | kΩ   |

| ESR              | Input and Output Capacitor Equivalent Series Resistance (ESR) | 5 to 100   | mΩ   |

### **Electrical Characteristics**

$(V_{IN} = V_{OUT} + 2V; I_{OUT} = 10 mA, C_{IN} = C_{OUT} = 2.2 \mu F, T_J = -40 ^{\circ}C \sim 125 ^{\circ}C$  unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}C.)$  (3)

| Symbol              | Parameter                           | Test Conditions                                                        | Min | Тур | Max | Unit  |

|---------------------|-------------------------------------|------------------------------------------------------------------------|-----|-----|-----|-------|

| $V_{IN}$            | Operating Input Voltage(4)          |                                                                        | 3.0 |     | 40  | V     |

| Vuvlo               | Lindar Valtaga Laak Out             | V <sub>IN</sub> Rising, I <sub>OUT</sub> =300mA                        |     | 2.5 |     | V     |

| Vuvlo_HYS           | Under Voltage Lock Out              | Hysteresis                                                             |     | 300 |     | mV    |

| ΙQ                  | Quiescent Current                   | $I_{OUT} = 0mA$                                                        |     | 7   |     | μA    |

| l                   | Ctandby Current                     | $V_{EN} = 0V$ , $V_{IN} = 4$ V, $T_A = 25$ °C                          |     | 1   | 1.7 |       |

| IQ_OFF              | Standby Current                     | $V_{EN} = 0V$ , $V_{IN} = 40V$ , $T_A = 25$ °C                         |     | 1.5 | 4   | μA    |

|                     |                                     | Iоит=300mA, Vоит=3.3V                                                  |     | 500 | 780 |       |

| \/                  | Dropout Voltago(5)                  | $T_A = +25$ °C                                                         | 500 |     | 760 | mV    |

| $V_{DROP}$          | Dropout Voltage <sup>(5)</sup>      | Iout=300mA, Vout=5V                                                    |     | 400 | 760 | IIIV  |

|                     |                                     | $T_A = +25$ °C                                                         |     | 480 | 760 | ļ     |

| Line <sub>REG</sub> | Line Regulation                     | $V_{OUT}+2V \le V_{IN} \le 40V$                                        | 0.4 |     |     | %/V   |

| LITIEREG            | Line Regulation                     | $I_{OUT} = 10mA$                                                       |     | 0.1 |     | 70/ V |

| Load <sub>REG</sub> | Lood Population                     | 1mA ≤ I <sub>OUT</sub> ≤ 300mA                                         |     | 15  |     | mV    |

| LUAUREG             | Load Regulation                     | $V_{IN} = V_{OUT} + 2V$                                                |     | 15  |     |       |

| $I_{LMT}$           | Current Limit                       | $V_{IN} = V_{OUT} + 2V$                                                |     | 530 |     | mA    |

| V <sub>ENH</sub>    | EN Pin Threshold Voltage            | EN Input Voltage "H"                                                   |     | 1.3 |     | V     |

| V <sub>ENL</sub>    | EN Pin Threshold Voltage            | EN Input Voltage "L"                                                   |     | 1.0 |     | V     |

| I <sub>EN</sub>     | EN Leakage Current                  | V <sub>EN</sub> =V <sub>EN_MAX</sub> , I <sub>OUT</sub> =300mA         |     | 0.2 |     | μA    |

| T <sub>ON</sub>     | Soft Start Time                     | From Enable to 90%V <sub>OUT_normal</sub>                              |     | 600 |     | us    |

|                     |                                     | $f = 100Hz$ , $V_{IN} = V_{OUT} + 2V$ ,                                |     | 100 |     | dB    |

|                     |                                     | $V_{OUT}=3.3V$ , $I_{OUT}=30mA$                                        |     | 100 |     | uБ    |

| PSRR                | Power Supply                        | $f = 1 \text{ kHz}, V_{IN} = V_{OUT} + 2V,$                            | 105 |     |     | dB    |

| FORK                | Rejection Ratio <sup>(6)</sup>      | $V_{OUT}=3.3V$ , $I_{OUT}=30mA$                                        |     | 105 |     | uБ    |

|                     |                                     | $f = 10 \text{ kHz}, V_{IN} = V_{OUT} + 2V,$                           | 70  |     |     | dB    |

|                     |                                     | $V_{OUT}=3.3V$ , $I_{OUT}=30mA$                                        |     |     |     | GD.   |

|                     |                                     | $V_{IN} = V_{OUT} + 2V$ , $I_{OUT} = 1mA$ ,                            |     |     |     |       |

| en                  | Output Noise Voltage <sup>(6)</sup> | f = 10Hz to $100KHz$ ,                                                 | 30  |     |     | μVrms |

|                     |                                     | C <sub>OUT</sub> = 1μF                                                 |     |     |     |       |

| $V_{PG\_R}$         | PG Rising Threshold                 | V <sub>OUT</sub> / V <sub>OUT_SET</sub> , when V <sub>OUT</sub> rising | 90  |     |     | %     |

| t <sub>D_PGR</sub>  | PG Rising Delay                     | From $V_{OUT} = 90\% \times V_{OUT(normal)}$                           |     | 400 |     | μs    |

| ים. פת              | . C Moning Dolay                    | to PG=High, C <sub>PGDL</sub> =0nf                                     | 400 |     |     | μ0    |

| $T_{SD}$            | Thermal Shutdown                    | Temperature Increasing                                                 | 145 |     |     | °C    |

| . 55                | Temperature <sup>(6)</sup>          | from T <sub>A</sub> =+25°C                                             |     |     |     |       |

| $T_{SDH}$           | Thermal Shutdown                    | Temperature Falling                                                    | 30  |     |     | °C    |

| - 5011              | Hysteresis <sup>(6)</sup>           | from T <sub>SD</sub>                                                   |     |     |     |       |

**Note3.** Here  $V_{IN}$  means internal circuit can work normal. If  $V_{IN} < V_{OUT}$ , Output voltage follows  $V_{IN}(I_{OUT}=1mA)$ , circuit is safety.

*Note4.* The minimum operating voltage is 3.0V.  $V_{DROP} = V_{IN(min)} - V_{OUT}$ .

Note5. Vdrop FT test method: test the Vout voltage at Vset+Vdropmax with 300mA output current.

Note6. Guaranteed by design and characterization. not a FT item.

### **Application Circuits**

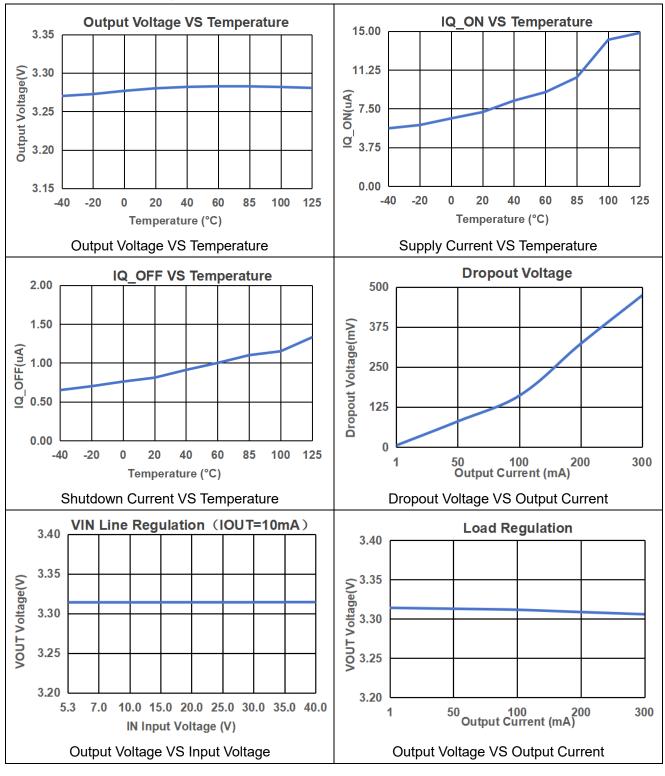

### **Typical Characteristics**

$V_{OUT} = 3.3V$

$(V_{IN} = V_{OUT} + 2V; I_{OUT} = 10 mA, C_{IN} = C_{OUT} = 2.2 \mu F, T_J = -40 ^{\circ} C \sim 125 ^{\circ} C$  unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ} C$ .)

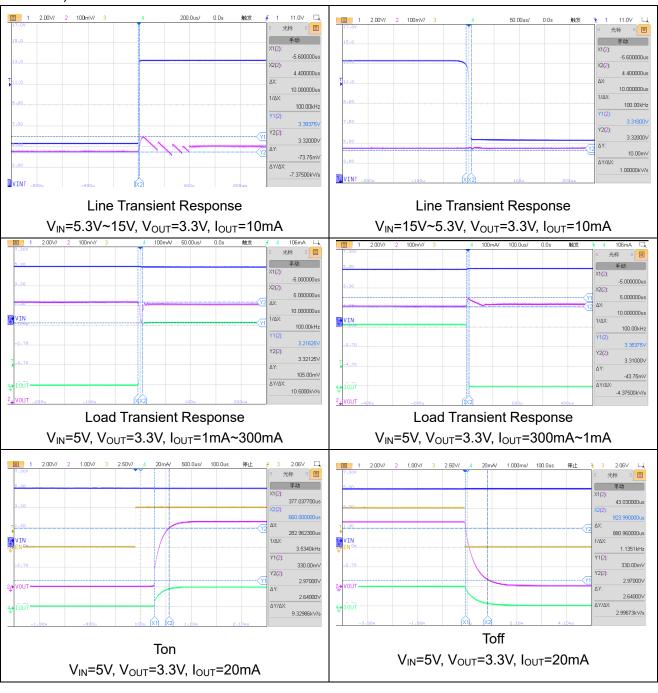

### **Typical Characteristics (Continued)**

#### $V_{OUT} = 3.3V$

$(V_{IN} = V_{OUT} + 2V; C_{IN} = C_{OUT} = 2.2 \mu F, T_J = -40 ^{\circ} C \sim 125 ^{\circ} C$  unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ} C$ .)

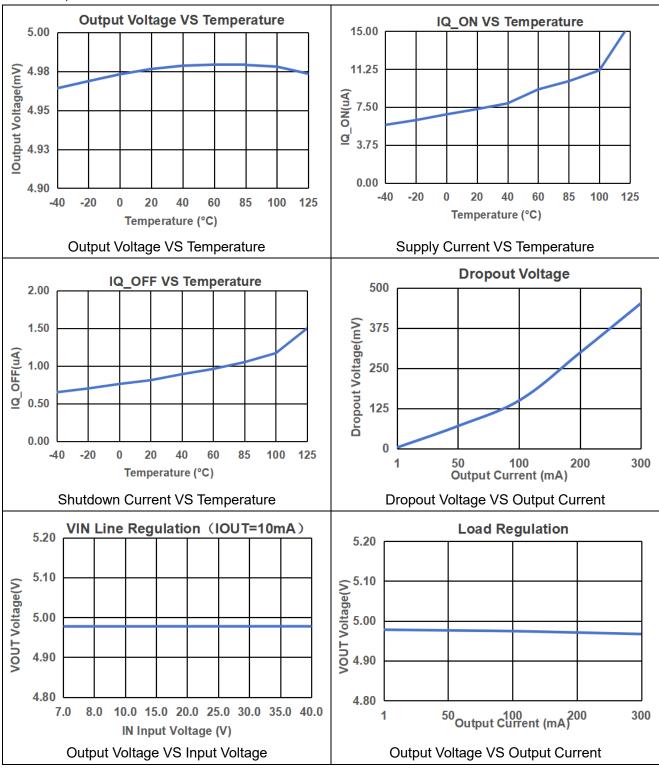

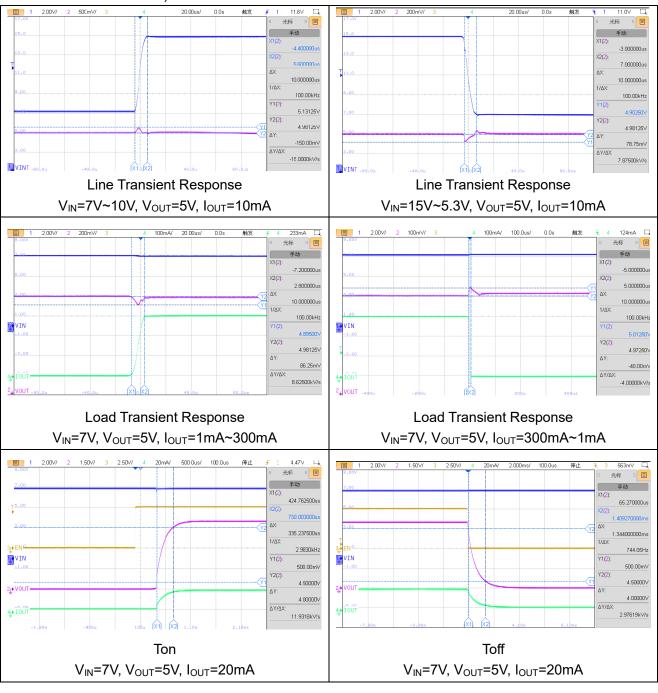

### **Typical Characteristics(Continued)**

#### $V_{OUT} = 5.0V$

$(V_{IN} = V_{OUT} + 2V; C_{IN} = C_{OUT} = 2.2\mu F, T_J = -40^{\circ}C \sim 125^{\circ}C$  unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

### **Typical Characteristics (Continued)**

#### $V_{OUT} = 5.0V$

$(V_{IN} = V_{OUT} + 2V; I_{OUT} = 10 \text{mA}, C_{IN} = C_{OUT} = 1.0 \mu\text{F}, T_J = -40 ^{\circ}\text{C} \sim 125 ^{\circ}\text{C}$  unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}\text{C}$ .)

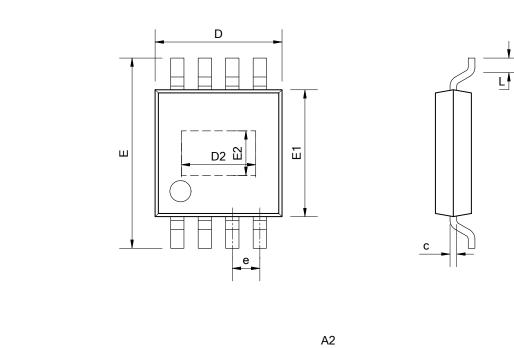

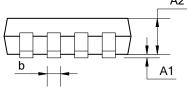

## **Package Dimension**

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN  | NOM  | MAX  |

|--------|------|------|------|

| A1     | 0.00 | ı    | 0.15 |

| A2     | 1.35 | 1.40 | 1.50 |

| b      | 0.38 | ı    | 0.47 |

| С      | 0.17 | ı    | 0.25 |

| D      | 4.80 | 4.90 | 5.00 |

| Е      | 5.80 | 6.00 | 6.20 |

| D2     | 3.02 | 3.17 | 3.32 |

| E1     | 3.80 | 3.90 | 4.00 |

| E2     | 2.13 | 2.28 | 2.43 |

| е      | 1.17 | 1.27 | 1.37 |

| L      | 0.45 | 0.60 | 0.80 |

## **Revision History and Checking Table**

| Version | Date       | Revision Item    | Modifier | Function & Spec<br>Checking | Package & Tape<br>Checking |  |

|---------|------------|------------------|----------|-----------------------------|----------------------------|--|

| 1.0     | 2025-07-01 | Original Version | Hucy     | Yangxx                      | Liujy                      |  |