# Precision, 20-MHz, 1-pA, Low-Noise, RRIO, CMOS Operational Amplifier

### **General Description**

ET85201 is a single low-voltage (1.8 V to 5.5 V) operational amplifier (op amp) with very low noise and wide bandwidth capabilities while operating on a low quiescent current of only 1.7 mA.

ET85201 is ideal for low-power, single-supply applications. Low-noise (7 nV/ $\sqrt{\text{Hz}}$ ) and high speed operation also make it well-suited for driving sampling analog-to-digital converters (ADCs). Other applications include signal conditioning and sensor amplification.

ET85201 features a linear input stage with zero-crossover distortion that delivers excellent common-mode rejection ratio (CMRR) of typically 114 dB over the full input range. The input common mode range extends 100 mV beyond the negative and positive supply rails. The output voltage typically swings within 10 mV of the rails.

#### **Features**

Precision with Zero-Crossover Distortion:

Low Offset Voltage: 250 μV (Maximum)

> High CMRR: 114 dB

> Rail-to-Rail I/O

Low noise: 7 nV/√Hz at 10 kHz

Wide Bandwidth: 20 MHz

Slew Rate: 10 V/μs

Quiescent Current: 1.7 mA/Ch

Single-Supply Voltage Range: 1.8 V to 5.5 V

Unity-Gain Stable

#### **Applications**

- High-Z Sensor Signal Conditioning

- Transimpedance Amplifiers

- Test and Measurement Equipment

- Programmable Logic Controllers (PLCs)

- Motor Control Loops

- Communications

- Input/Output ADC/DAC Buffers

- Active Filters

## **Device information**

| Part No. |           | Package | Packing Option          | MSL |

|----------|-----------|---------|-------------------------|-----|

|          | ET85201EA | SOT23-5 | Tape and Reel , 3k/Reel | 3   |

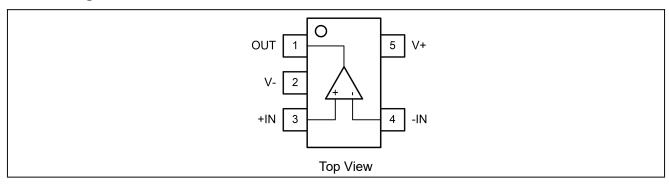

# Pin Configuration

## **Pin Function**

| Pin Number | Symbol          | Descriptions        |

|------------|-----------------|---------------------|

| 1          | 1 OUT           |                     |

| 2          | V-              | Negative supply     |

| 3          | +IN             | Non-inverting input |

| 4          | -IN Inverting i |                     |

| 5          | V+              | Positive supply     |

## **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are only stress ratings, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions are not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| Symbol              | Parameter                                     | Value                | Unit |

|---------------------|-----------------------------------------------|----------------------|------|

| Vs                  | Supply Voltage                                | 0 to 6               | V    |

| V <sub>IN</sub>     | Signal input terminals Voltage <sup>(1)</sup> | (V-)-0.5 to (V+)+0.5 | V    |

| I <sub>IN</sub>     | Signal input terminals Current <sup>(1)</sup> | -10 to +10           | mA   |

| I <sub>SC</sub>     | Output short-circuit Current <sup>(2)</sup>   | Continuous           | mA   |

|                     | ESD (Human Body Model)                        | ±4000                | V    |

| V <sub>ESD</sub>    | ESD (Component Discharge Model)               | ±1000                | V    |

|                     | ESD (Machine Model)                           | ±200                 | V    |

| T <sub>STG</sub>    | Storage Temperature Range                     | -65 to +150          | °C   |

| T <sub>J(MAX)</sub> | Max Junction Temperature Range                | +150                 | °C   |

| T <sub>A</sub>      | Operating Temperature Range                   | -40 to +125          | °C   |

**Note1**: Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5 V beyond the supply rails should be current limited to 10 mA or less.

Note 2: Short-circuit to ground, one amplifier per package.

#### **Thermal Characteristics**

| Symbol Package   |         | Ratings                                                      | Value | Unit         |

|------------------|---------|--------------------------------------------------------------|-------|--------------|

| R <sub>θJA</sub> | SOT23-5 | Thermal Characteristics, Thermal Resistance, Junction-to-Air | 219.3 | Unit<br>°C/W |

## **Recommended Operating Conditions**

| Symbol         | Parameter                   | Value                  | Unit |

|----------------|-----------------------------|------------------------|------|

| Vs             | Supply Voltage: (V+) - (V-) | 1.8(±0.9) ~ 5.5(±2.75) | V    |

| T <sub>A</sub> | Operating Temperature Range | -40 ~ +125             | °C   |

# **Electrical Characteristics**

$V_S$  = (V+) – (V-) = 1.8 V to 5.5 V (±0.9 V to ±2.75 V),  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$  connected to  $V_S/2$ , and  $V_{CM}$  =  $V_{OUT}$  =  $V_S/2$  (unless otherwise noted)

| Symbol               | Parameter                                  | Conditions                                                                                               | Min      | Тур  | Max      | Unit             |  |

|----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------|----------|------|----------|------------------|--|

| OFFSET               | VOLTAGE                                    |                                                                                                          |          |      |          |                  |  |

| Vos                  | Input offset voltage                       |                                                                                                          |          | ±60  | ±250     | μV               |  |

| ΔV <sub>OS</sub> /ΔT | Input offset voltage vs temperature        | $V_S = 5.5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                                               |          | ±1.5 | ±5       | μV/°C            |  |

| PSRR                 | Input offset voltage vs power supply       | V <sub>S</sub> = 1.8 to 5.5 V                                                                            |          | ±5   | ±20      | μV/V             |  |

| INPUT V              | OLTAGE RANGE                               |                                                                                                          |          |      | -1       | ı                |  |

| V <sub>CM</sub>      | Common-mode voltage range                  | V <sub>S</sub> = 1.8 V to 5.5 V                                                                          | (V-)-0.1 |      | (V+)+0.1 | V                |  |

| CMRR                 | Common-mode rejection ratio                | $V_S = 5.5 \text{ V},$<br>(V-) - 0.1 V < $V_{CM}$ < (V+) + 0.1 V                                         | 100      | 114  |          | dB               |  |

| INPUT B              | IAS CURRENT                                |                                                                                                          |          |      |          |                  |  |

| I <sub>B</sub>       | Input bias current <sup>(3)</sup>          | T <sub>A</sub> = 25°C                                                                                    |          | ±1   |          | pА               |  |

| los                  | Input offset current(3)                    | T <sub>A</sub> = 25°C                                                                                    |          | ±1   |          | рА               |  |

| NOISE                |                                            |                                                                                                          |          |      | •        |                  |  |

| En                   | Input voltage noise<br>(peak to peak)      | f = 0.1 Hz to 10 Hz                                                                                      |          | 2.8  |          | μV <sub>PP</sub> |  |

|                      | Input voltage                              | f = 1 kHz                                                                                                |          | 8.5  |          |                  |  |

| en                   | noise density                              | f = 10 kHz                                                                                               |          | 7    |          | -nV/√Hz          |  |

| İn                   | Input current noise density <sup>(3)</sup> | f = 1 kHz                                                                                                |          | 0.6  |          | fA/√Hz           |  |

| INPUT C              | APACITANCE                                 |                                                                                                          |          |      |          |                  |  |

| C <sub>ID</sub>      | Differential                               |                                                                                                          |          | 5    |          | pF               |  |

| C <sub>IC</sub>      | Common-mode                                |                                                                                                          |          | 4    |          | pF               |  |

| OPEN-L               | OOP GAIN                                   |                                                                                                          |          |      |          |                  |  |

| ۸                    | A <sub>OL</sub> Open-loop voltage gain     | $0.1 \text{ V} < V_0 < (V+) - 0.1 \text{ V},$ $R_L = 10 \text{ k}\Omega,$                                | 114      | 128  |          | dВ               |  |

| AOL                  |                                            | $0.2 \text{ V} < \text{V}_{\text{O}} < (\text{V+}) - 0.2 \text{ V},$ $R_{\text{L}} = 2 \text{ k}\Omega,$ | 108      | 125  |          | dB               |  |

| PM                   | Phase margin                               | $V_{S} = 5 \text{ V, } C_{L} = 50 \text{pF}$                                                             |          | 47   |          | 0                |  |

# **Electrical Characteristics (Continued)**

| Symbol                     | Parameter                                                       | Conditions                                                                    | Min        | Тур    | Max         | Unit |  |  |

|----------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------|------------|--------|-------------|------|--|--|

| FREQUE                     | FREQUENCY RESPONSE,V <sub>S</sub> = 5 V, C <sub>L</sub> = 50 pF |                                                                               |            |        |             |      |  |  |

| GBP Gain-bandwidth product |                                                                 | Unity gain                                                                    |            | 20     |             | MHz  |  |  |

| SR                         | Slew rate                                                       | G =+1                                                                         |            | 10     |             | V/µs |  |  |

| 1                          | C-441:                                                          | To 0.1%,2V step,<br>G = +1                                                    |            | 0.25   |             |      |  |  |

| ts                         | Settling time <sup>(3)</sup>                                    | To 0.01%, 2V step,<br>G = +1                                                  |            | 0.32   |             | μs   |  |  |

| t <sub>OR</sub>            | Overload recovery time                                          | V <sub>IN</sub> × gain > V <sub>S</sub>                                       |            | 100    |             | ns   |  |  |

| THD+N                      | Total harmonic                                                  | $V_{O} = 4 V_{pp}, G = 1, f = 1 \text{ kHz},$ $R_{L} = 10 \text{ k}\Omega$    |            | 0.0004 |             | %    |  |  |

| I HU+IN                    | distortion + noise                                              | $V_{O} = 2 V_{pp}, G = 1, f = 1 \text{ kHz},$ $R_{L} = 600\Omega$             |            | 0.0005 |             | %    |  |  |

| OUTPUT                     | -                                                               |                                                                               |            |        |             |      |  |  |

|                            |                                                                 | R <sub>L</sub> = 10 kΩ, T <sub>A</sub> = 25°C                                 |            | 10     | 20          | mV   |  |  |

| Vo                         | Voltage output swing from supply rails                          | $R_L = 2 k\Omega, T_A = 25^{\circ}C$                                          |            | 25     | 35          |      |  |  |

| VO                         |                                                                 | $R_L = 10 \text{ k}\Omega, T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |            |        | 30          |      |  |  |

|                            |                                                                 | $R_L = 2 \text{ k}\Omega, T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$  |            |        | 45          |      |  |  |

| I <sub>SC</sub>            | Short-circuit current                                           | V <sub>S</sub> = 5.5 V                                                        |            | ±70    |             | mA   |  |  |

| Zo                         | Open-loop<br>output impedance <sup>(3)</sup>                    | I <sub>O</sub> = 0mA, <i>f</i> = 1MHz                                         |            | 90     |             | Ω    |  |  |

| POWER SUPPLY               |                                                                 |                                                                               |            |        |             |      |  |  |

| Vs                         | Specified voltage range                                         |                                                                               | 1.8 (±0.9) |        | 5.5 (±2.75) | V    |  |  |

|                            | 0.1                                                             | $I_0 = 0 \text{ mA}, V_S = 5.5 \text{ V}$                                     |            | 1.7    | 2.0         |      |  |  |

| ΙQ                         | Quiescent current per amplifier                                 | $I_0 = 0$ mA, $V_S = 5.5$ V,<br>$T_A = -40$ °C to 125°C                       |            |        | 2.15        | mA   |  |  |

Note3:Guaranteed by design.

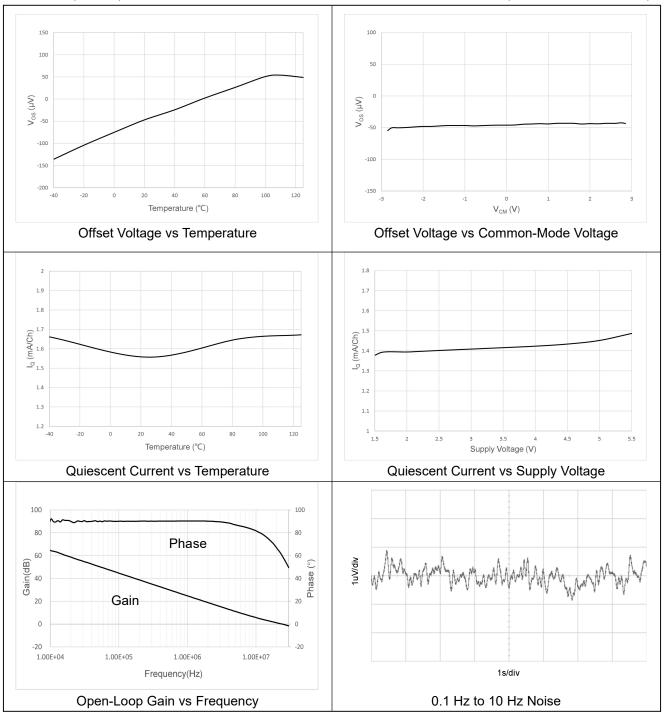

## **Typical Characteristics**

$V_S = 5.5 \text{ V}(\pm 2.75 \text{V}), V_{CM} = V_{OUT} = V_S/2, \text{ and } R_L = 10 \text{k}\Omega \text{ connected to } V_S/2, T_A = 25 ^{\circ}\text{C} \text{ (unless otherwise noted)}$

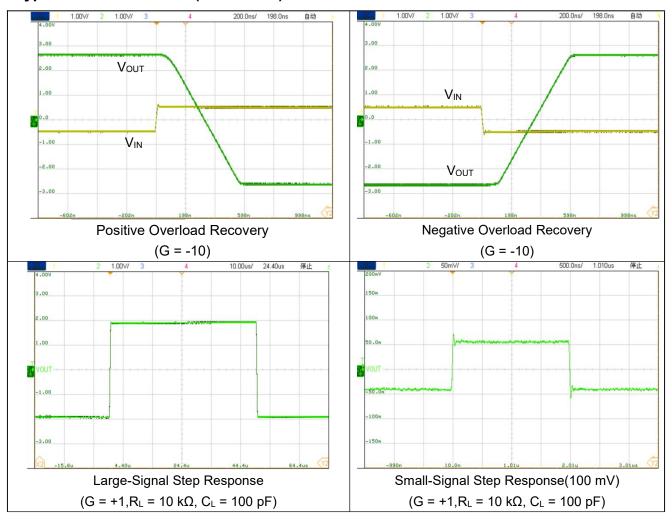

## **Typical Characteristics (Continued)**

#### **Functional Description**

#### Overview

ET85201 is a high-speed, precision amplifier, perfectly suited to drive 12-, 14-, and 16-bit analog-to-digital converters. Low output impedance with flat frequency characteristics and zero-crossover distortion circuitry enable high linearity over the full input common mode range, achieving true rail-to-rail input from a 1.8 V to 5.5 V single supply.

#### **Operating Voltage**

ET85201 is unity-gain stable and can operate on a single-supply voltage (1.8 V to 5.5 V), or a split-supply voltage ( $\pm 0.9$  V to  $\pm 2.75$  V), making it highly versatile and easy to use. The power-supply pins should have local bypass ceramic capacitors (typically 0.001  $\mu$ F to 0.1  $\mu$ F). ET85201 is fully specified from 1.8 V to 5.5 V and over the extended temperature range of -40°C to 125°C.

#### Rail-to-Rail Input

ET85201 features true rail-to-rail input operation, with supply voltages as low as ±0.9 V (1.8 V). ET85201 includes an internal charge-pump that powers the amplifier input stage with an internal supply rail at approximately 1.6 V above the external supply (Vs+). This internal supply rail allows the single differential input pair to operate and remain very linear over a very wide input common mode range. A unique zero-crossover input topology eliminates the input offset transition region typical of many rail-to-rail, complementary input stage operational amplifiers. This topology allows the ET85201 to provide superior common-mode performance (CMRR > 110 dB, typical) over the entire common-mode input range, which extends 100 mV beyond both power-supply rails. When driving analog-to-digital converters (ADCs), the highly linear VcM range of the ET85201 assures maximum linearity and lowest distortion.

#### **Capacitive Load and Stability**

ET85201 is designed to be used in applications where driving a capacitive load is required. As with all op amps, there may be specific instances where the ET85201 can become unstable. The particular op amp circuit configuration, layout, gain, and output loading are some of the factors to consider when establishing whether an amplifier is stable in operation. An op amp in the unity-gain (1-V/V) buffer configuration and driving a capacitive load exhibits a greater tendency to become unstable than an amplifier operated at a higher noise gain. The capacitive load, in conjunction with the op amp output resistance, creates a pole within the feedback loop that degrades the phase margin. The degradation of the phase margin increases as the capacitive loading increases. When operating in the unity-gain configuration, ET85201 remains stable with a pure capacitive load up to approximately 1 nF.

#### **Layout Guidelines**

ET85201 is a wideband amplifier. To realize the full operational performance of the device, good high frequency PCB layout practices are required. The bypass capacitors must be connected between each supply pin and ground as close to the device as possible. The bypass capacitor traces should be designed for minimum inductance.

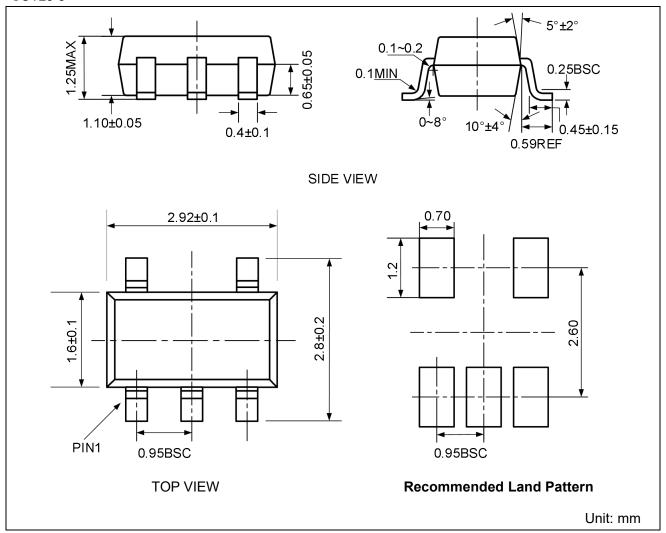

## **Package Dimension**

## SOT23-5

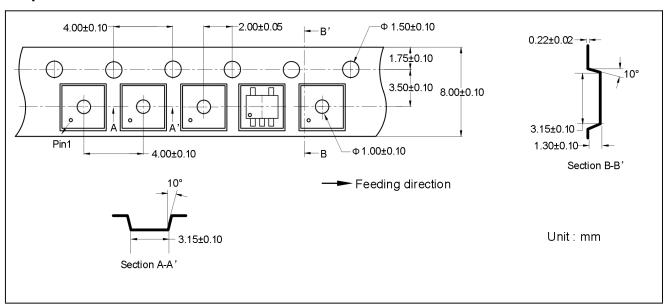

# **Tape Information**

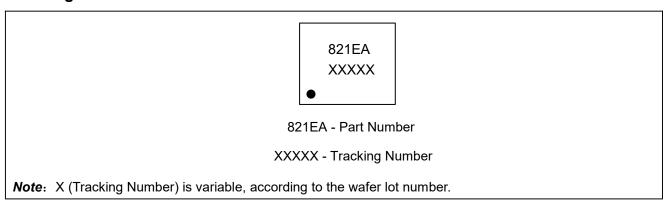

## **Marking Information**

# **Revision History and Checking Table**

| Version | Date       | Revision Item    | Modifier | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|------------------|----------|-----------------------------|----------------------------|

| 1.0     | 2025-06-18 | Original Version | Huyt     | Jiangxw                     | Liujy                      |

|         |            |                  |          |                             |                            |

|         |            |                  |          |                             |                            |